#### **RISC-V Developers Forum**

7 декабря, Москва

# Генератор тестовых программ MicroTESK for RISC-V

#### Андрей Татарников

Институт системного программирования им. В.П. Иванникова Российской академии наук

#### Введение

#### Тестирование микропроцессоров

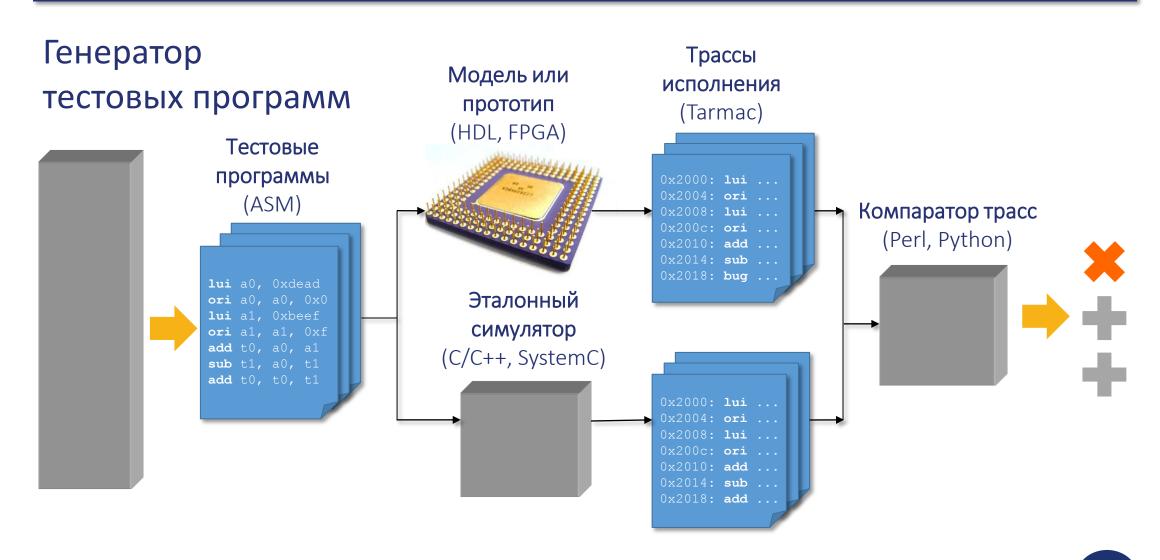

# Генератор

# Основные требования

- Не должно быть

- нарушений предусловий: UNPREDICTABLE

- обращений к неинициализированным данным

- зацикливаний в тестовых программах

- Должна быть возможность

- покрытия интересных ситуаций (corner cases)

- создания встроенных проверок (self-checks)

#### MicroTESK

#### Генератор тестовых программ

#### Язык nML

#### Типы, регистры и режимы доступа

```

// Константы

#ifdef RV64I

let XLEN = 64

#else

let XLEN = 32

#endif

let MEM SIZE = 2 ** (XLEN - 2)

// Типы данных

type BYTE = card(8) // Unsigned

type WORD = card(32) // Unsigned

type XWORD = card(XLEN)

// Unsigned

type XINT = int(XLEN)

// Signed

. . .

```

```

// Регистры и псевдонимы

reg XREG [32, XWORD] // 32 peructpa XWORD

reg SP[XWORD] alias = XREG[2]

req PC[XWORD]

// Режимы доступа к регистрам

mode REG(i: card(5)) = XREG[i]

syntax = format("x%d", i) // E.g. x13

image = format("%5s", i) // E.g. 01101

```

```

// Массив физической памяти mem MEM [MEM SIZE, WORD]

```

3

#### Язык nML

#### Операции и их группы

```

// Операция сложения

op add(rd: X, rs1: X, rs2: X)

syntax = format("add %s, %s, %s",

rd.syntax, rs1.syntax, rs2.syntax)

image = format("0000000%s%s000%s0110011",

rs2.image, rs1.image, rd.image)

action = { // Семантика инструкции

rd = rs1 + rs2;

// Операция ветвления

op beg(rs1: X, rs2: X, imm: card(12))

syntax = format("beq %s, %s, %<label>d", ...)

image = ...

action = {

if rs1 == rs2 then

PC = PC + (sign extend(XWORD, imm) << 1);</pre>

endif;

```

```

// Группы операций (ИЛИ-правила)

ор ALU = ADD | ...

ор BPU = BEQ | ...

ор Op = ALU | BPU | ...

```

```

// Композиция операций (И-правило)

op instruction(operation: Op)

syntax = operation.syntax

image = operation.image

action = {

XREG[0] = 0;

prev_pc = PC;

operation.action;

if PC == prev_pc then

PC = PC + 4;

endif;

}

```

### Язык Ruby Шаблоны тестовых программ

```

class MyTemplate < RiscVBaseTemplate</pre>

def run

block(:combinator => 'product',

:compositor => 'random') {

iterate {

xor x(), x(_), x(_)

lui x(),

iterate {

and x(), x(), x()

or x(), x(), x()

iterate {

auipc x(),

.run

end

end

```

#### Всего $2 \times 2 \times 1 = 4$ тестовых примера

```

# Инициализация

ori a7, a7, 0x2d7

slli a7, a7, 0xb

ori a7, a7, 0x1

slli a7, a7, 0xb

ori a7, a7, 0x3d2

ori t3, t3, 0x164

slli t3, t3, 0xb

ori t3, t3, 0x52b

slli t3, t3, 0xb

ori t3, t3, 0x24e

# Тестовое воздействие

and s4, a7, a7

xor s8, s4, t3

auipc t2, 0xafc37

```

### Язык Ruby Инициализирующий код

```

# Инициализация регистров Х

preparator(:target => 'X') {

if rv64i then

ori target, zero, value(53, 63)

slli target, target, 11

ori target, target, value (42, 52)

slli target, target, 11

ori target, target, value(32, 41)

slli target, target, 10

end

ori target, target, value(21, 31)

slli target, target, 11

ori target, target, value(10, 20)

slli target, target, 11

ori target, target, value(0, 9)

```

```

# Оптимизированная инициализация регистров

preparator (

:target => 'X',

:mask => "000000000000000") {

or target, zero, zero

preparator (

:target => 'X',

:mask => "FFFFFFFFFFFF") {

nor target, zero, zero

```

```

# Инициализация памяти

memory preparator(:size => 64) {

prepare t1, value

prepare t2, address

sd t1, t2, 0

```

# MicroTESK Поддерживаемые техники генерации

- Тестовые данные (значения операндов)

- Случайная генерация (range, dist, ...)

- Разрешение ограничений (внешние **SMT-решатели**)

- Тестовые последовательности (потоки инструкций)

- Комбинаторная генерация (combinator, compositor, ...)

- Специализированные генераторы (branch, memory, ...)

#### MicroTESK Заключение

- Высокая автоматизация на базе спецификаций

- Гибкая настройка на разные архитектуры

- Расширяемость

- Поддержка RISC-V

- Open source

- Применяется в реальных проектах

| Архитектура                                                                                                                                   | RISC-V         |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| RISC-V Instruction Set Manual<br>Volume I: User-Level ISA (v. 2.2)<br>RV32I, RV64I, RV32M, RV64M, RV32A,<br>RV64A, RV32F, RV64F, RV32D, RV64D | 145 страниц    |

| Поддерживаемые инструкции                                                                                                                     | 201 инструкция |

| Спецификации ISA (nML)                                                                                                                        | 2300 строк     |

### MicroTESK Планы на будущее

- Повышение уровня автоматизации генерации

- Online-генерация тестовых программ

- Оценка тестового покрытия на уровне архитектуры

- Статический анализ и верификация бинарного кода

#### MicroTESK Контакты

#### Overview

MicroTESK is a reconfigurable (retargetable and extendable) model-based test program generator (TPG) for microprocessors and other programmable devices (such kind of tools are also called instruction stream generators or ISG). The generator is customized with the help of instruction-set architecture (ISA) specifications and configuration files, which describe parameters of the microprocessor subsystems (pipeline, memory and others). The suggested approach eases the model development and makes it possible to apply the model-based testing in the early design stages when the microprocessor architecture is frequently modified.

The current version of the tool supports ISA specification (in nML) and manual development of test program templates (in @ Ruby). It also implements lightweight methods for automated test program generation, including random-based and combinatorial techniques. Facilities for describing memory management units and microprocessor pipelines (microarchitectural networks) are under development, and so are the methods for advanced test program generation. The framework is applicable to a wide range of microprocessor architectures including RISC (ARM, MIPS, SPARC, etc.), CISC (x86, etc.), VLIW/EPIC (Elbrus, Itanium, etc.), DSP, GPII etc

http://www.microtesk.org/

http://forge.ispras.ru/projects/microtesk-riscv

https://www.facebook.com/MicroTESK

microtesk-support@ispras.ru

#### Спасибо

#### Вопросы?